### **General Description**

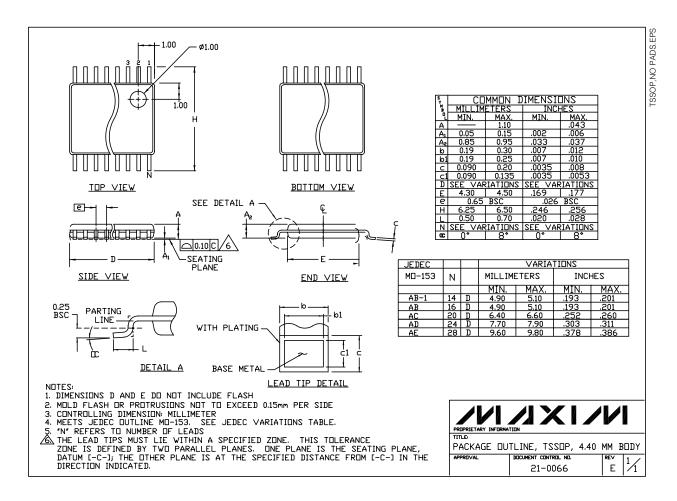

The MAX5426 is a precision resistor network optimized for use with programmable instrumentation amplifiers. The MAX5426 operates from dual ±5V to ±15V supplies and consumes less than 40µA of supply current. Designed to be used in the traditional three op amp instrumentation amplifier topology, this device provides noninverting gains of 1, 2, 4, and 8 that are accurate to 0.025% (A-grade), 0.09% (B-grade), or 0.5% (C-grade) over the extended temperature range (-40°C to +85°C). The MAX5426 is available in the 6.4mm x 5mm 14-pin TSSOP package.

### **Applications**

General-Purpose Programmable Instrumentation **Amplifiers**

Gain Control in RF Power Amplifiers Precision Dual Attenuator

#### **Features**

- ◆ Differential Gains: Ay = 1, 2, 4, 8

- ♦ Gain Accurate to 0.025%, 0.09%, or 0.5%

- ♦ Dual Supply ±5V to ±15V Operation

- ♦ Low 36µA Supply Current

- **♦ Simple CMOS/TTL Logic Compatible 2-Wire Parallel Interface**

- ♦ Space-Saving 14-Pin TSSOP Package  $(6.4mm \times 5mm)$

- ♦ OFFSET Pin Available to Offset the Output of the **Differential Amplifier**

#### **Ordering Information**

| PART        | TEMP<br>RANGE  | PIN-<br>PACKAGE | GAIN   |

|-------------|----------------|-----------------|--------|

| MAX5426AEUD | -40°C to +85°C | 14 TSSOP        | 0.025% |

| MAX5426BEUD | -40°C to +85°C | 14 TSSOP        | 0.09%  |

| MAX5426CEUD | -40°C to +85°C | 14 TSSOP        | 0.5%   |

Pin Configuration and Functional Diagram appear at end of data sheet.

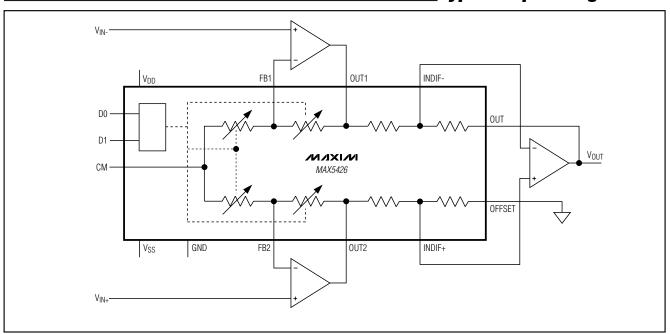

### **Typical Operating Circuit**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND         | 0.3V to +17V                           |

|--------------------------------|----------------------------------------|

| V <sub>SS</sub> to GND         | 17V to +0.3V                           |

| D0, D1 to GND                  | 0.3V to $(V_{DD} + 0.2V)$              |

| D0, D1 to GND $(V_{DD} > +6V)$ | 0.3V to +6.0V                          |

| All Other Pins to GND          | $(V_{SS} - 0.3V)$ to $(V_{DD} + 0.2V)$ |

| Maximum Current Into VDD, VSS, | D1, D0±50mA                            |

| Maximum Current from OUT1 to   | CM or OUT2±0.72mA                      |

| Maximum Current from OUT1 to INDIF- or C              | )UT±0.72mA     |

|-------------------------------------------------------|----------------|

| Maximum Current from OUT2 to INDIF+ or 0              | OFFSET±0.72mA  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) | )              |

| 14-Pin TSSOP (derate 9.1mW/°C above +                 | 70°C)727mW     |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 60°C to +150°C |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +15V, V_{SS} = -15V, GND = 0, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                            | SYMBOL                                | CONDITIONS                | MIN | TYP   | MAX   | UNITS |

|--------------------------------------|---------------------------------------|---------------------------|-----|-------|-------|-------|

|                                      |                                       | MAX5426A                  |     | 0.004 | 0.025 |       |

| Gain Range Accuracy (Notes 1, 2)     |                                       | MAX5426B                  |     | 0.025 | 0.090 | %     |

|                                      |                                       | MAX5426C                  |     | 0.080 | 0.500 |       |

| Capacitance at Analog Pins           | Canalog                               |                           |     | 5     |       | рF    |

|                                      |                                       | Gain = 1                  |     | 79    |       |       |

| Differential CMPP (Notes 1, 2)       |                                       | Gain = 2                  |     | 85    |       | -ID   |

| Differential CMRR (Notes 1, 2)       |                                       | Gain = 4                  |     | 91    |       | dB    |

|                                      |                                       | Gain = 8                  |     | 97    |       |       |

| DIGITAL INPUTS                       |                                       |                           |     |       |       |       |

| Input High Voltage                   | V <sub>IH</sub>                       |                           | 2.4 |       |       | V     |

| Input Low Voltage                    | VIL                                   |                           |     |       | 0.8   | V     |

| Input Leakage Current                | I <sub>LK</sub> G                     | D1 = D0 = 0 or logic high |     |       | 10    | μΑ    |

| EQUIVALENT RESISTANCES               |                                       |                           |     |       |       |       |

| Resistance Between OUT1 and OUT2     | R <sub>OUT1</sub> , R <sub>OUT2</sub> |                           |     | 56    |       | kΩ    |

| Resistance Between OUT1 and INDIF-   | ROUT1, RINDIF-                        |                           |     | 26    |       | kΩ    |

| Resistance Between INDIF- and OUT    | RINDIF-, ROUT                         |                           |     | 26    |       | kΩ    |

| Resistance Between OUT2 and INDIF+   | ROUT2, RINDIF+                        |                           |     | 26    |       | kΩ    |

| Resistance Between INDIF+ and OFFSET | R <sub>INDIF+</sub> ,<br>ROFFSET      |                           |     | 26    |       | kΩ    |

|                                      | ROUT1, RFB1                           | Gain = 1                  |     | 0     |       | kΩ    |

| Resistance Between OUT1 and          |                                       | Gain = 2                  |     | 15    |       |       |

| FB1                                  |                                       | Gain = 4                  |     | 22    |       |       |

|                                      |                                       | Gain = 8                  |     | 26    |       |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +15V, V_{SS} = -15V, GND = 0, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                               | SYMBOL                               | CONDITIONS   | MIN TYP N | IAX UNITS |

|-----------------------------------------|--------------------------------------|--------------|-----------|-----------|

| D : 1                                   | R <sub>FB1</sub> , R <sub>FB2</sub>  | Gain = 2     | 29        |           |

| Resistance Between FB1 and FB2 (Note 3) |                                      | Gain = 4     | 15        | kΩ        |

| (14016-3)                               |                                      | Gain = 8     | 7         |           |

|                                         |                                      | Gain = 1     | 0         |           |

| Resistance Between OUT2 and             | Douge Dena                           | Gain = 2     | 15        | kΩ        |

| FB2                                     | R <sub>OUT2</sub> , R <sub>FB2</sub> | Gain = 4     | 22        | K12       |

|                                         |                                      | Gain = 8     | 26        |           |

| Input Impedance at FB1                  | Z <sub>FB1</sub>                     |              | 0         | kΩ        |

| Input Impedance at FB2                  | Z <sub>FB2</sub>                     |              | 0         | kΩ        |

|                                         |                                      | Gain = 1     | 0         |           |

| Input Impedance at OUT1                 | 70.17.                               | Gain = 2     | 9.5       | kΩ        |

| (Note 4)                                | Z <sub>OUT1</sub>                    | Gain = 4     | 12        | K12       |

|                                         |                                      | Gain = 8     | 13        |           |

|                                         |                                      | Gain = 1     | 0         |           |

| Input Impedance at OUT2                 | Z <sub>OUT2</sub>                    | Gain = 2     | 9.5       | kΩ        |

| (Note 4)                                |                                      | Gain = 4     | 12        | NS2       |

|                                         |                                      | Gain = 8     | 13        |           |

| Input Impedance at INDIF+ (Note 4)      | Z <sub>INDIF+</sub>                  |              | 0         | kΩ        |

| Input Impedance at INDIF-<br>(Note 4)   | Z <sub>INDIF</sub> -                 |              | 0         | kΩ        |

| Input Impedance at OUT (Note 4)         | Zout                                 |              | 26        | kΩ        |

| Input Impedance at OFFSET (Note 4)      | Zoffset                              |              | 26        | kΩ        |

| POWER REQUIREMENTS                      | I                                    |              | <b>-</b>  |           |

| Positive Power-Supply Voltage           | $V_{DD}$                             |              | 4.75      | 5.75 V    |

| Negative Power-Supply Voltage           | V <sub>SS</sub>                      |              | -15.75 -4 | 1.75 V    |

| Positive Supply Current                 | I <sub>DD</sub>                      | D1 = D0 = 0  | 10        |           |

|                                         |                                      | D1 = D0 = 5V | 36        | μA        |

| Negative Supply Current                 | I <sub>SS</sub>                      |              | 0.01      | 10 μΑ     |

| TIMING REQUIREMENTS                     |                                      |              | ·         | •         |

| Switching Time (Note 5)                 | tswitching                           | (Figure 3)   | 60        | ns        |

- Note 1: Total error when configured as instrumentation amplifier. Assumes ideal op amps.

- Note 2: Each stage (input stage and output stage) is tested for accuracy separately and combined to give the total gain accuracy. The input stage is tested as follows: OUT1 = 10V, OUT2 = 0. Output stage is tested as follows: OUT1 = 10V, OUT2 = 0 and OUT2 = 10V, OFFSET = 0.

- **Note 3:** Gain of 1 configuration is open circuit (infinite impedance).

- Note 4: Equivalent load at each pin is calculated according to instrumentation amplifier configuration and assumes ideal op amps.

- Note 5: See Timing Diagram.

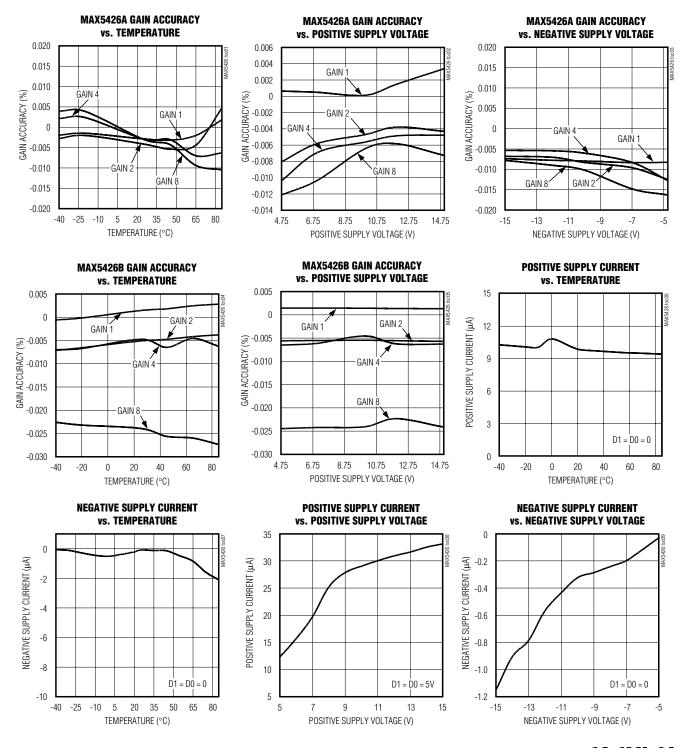

### **Typical Operating Characteristics**

$(V_{DD} = +15V, V_{SS} = -15V, T_A = +25$ °C, unless otherwise noted.)

### **Pin Description**

| PIN    | NAME            | FUNCTION                                                                                                                                      |  |  |  |

|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1      | $V_{DD}$        | Positive Power Supply. Bypass V <sub>DD</sub> to GND with a 0.1µF capacitor.                                                                  |  |  |  |

| 2      | GND             | Ground                                                                                                                                        |  |  |  |

| 3      | V <sub>SS</sub> | Negative Power Supply. Bypass VSS to GND with a 0.1µF capacitor.                                                                              |  |  |  |

| 4      | FB2             | First Stage Positive Input Terminal Resistor. Connect to the inverting terminal of the second input buffer (see Figure 1).                    |  |  |  |

| 5      | OUT2            | First Stage Positive Output Terminal Resistor. Connect to the output terminal of the second input buffer.                                     |  |  |  |

| 6      | OFFSET          | Second Stage Offset Terminal. Connect to a DC voltage to offset the output of the differential amplifier.                                     |  |  |  |

| 7      | INDIF-          | Second Stage Negative Input Terminal Resistor. Connect to the inverting input terminal of the differential op amp.                            |  |  |  |

| 8      | INDIF+          | Second Stage Positive Input Terminal Resistor. Connect to the noninverting input terminal of the differential op amp.                         |  |  |  |

| 9      | OUT             | Second Stage Output Terminal, Final Output Terminal                                                                                           |  |  |  |

| 10     | OUT1            | First Stage Negative Output Terminal of Resistor. Connect to the output terminal of the first input buffer.                                   |  |  |  |

| 11     | FB1             | First Stage Negative Input Terminal of Resistor. Connect to the inverting input terminal of the first input buffer.                           |  |  |  |

| 12     | CM              | Common-Mode Voltage. CM is the input common-mode voltage of the instrumentation amplifier. Typically varies ±1% of input common-mode voltage. |  |  |  |

| 13, 14 | D0, D1          | Digital Inputs. See Table 1.                                                                                                                  |  |  |  |

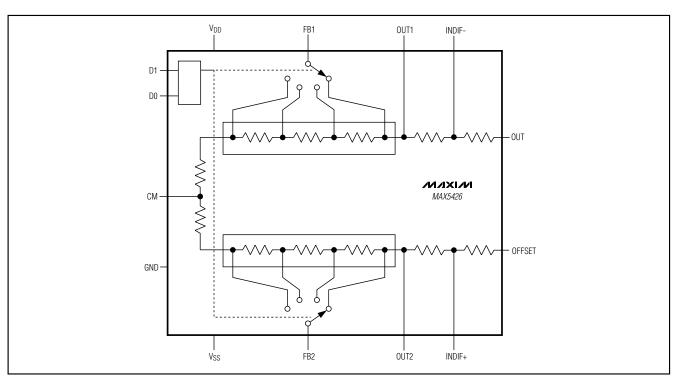

#### **Detailed Description**

The MAX5426 is a precision resistor network with low temperature drift and high accuracy that performs the same function as a precision resistor array and CMOS switches. Operationally, this device consists of fixed resistors and digitally controlled variable resistors that provide differential gains of 1, 2, 4, and 8 (see *Functional Diagram*). The MAX5426 provides gains accurate to 0.025% (MAX5426A), 0.09% (MAX5426B) or 0.5% (MAX5426C).

The MAX5426 is ideal for programmable instrumentation amplifiers. An offset pin is available to apply a DC offset voltage to the output of the differential amplifier. Pin CM is the common-mode input voltage and can be buffered and connected to the common-mode input of the instrumentation amplifier (usually the shield of the input cable to reduce the effects of cable capacitance and leakage).

#### **Digital Interface Operation**

The MAX5426 features a simple two-bit parallel programming interface. D1 and D0 program the gain setting according to the *Logic-Control Truth Table* (see Table 1). The digital interface is CMOS/TTL logic compatible.

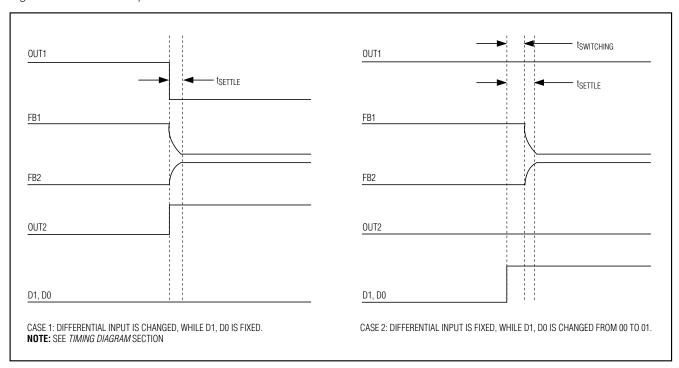

### Timing Diagram

Figure 3 shows the timing diagram of MAX5426 for two cases. In case 1, the differential input changes are at OUT1 and OUT2, while the voltage settling is observed at FB1 and FB2. The settling time (tSETTLE) is defined as the time for the output voltage (from the change in the input) to reach (and stay) within 0.02% of its final value.

In case 2, the differential inputs (OUT1 and OUT2) are at constant voltages, while D1 and D0 are varied (for example from 01 to 10) to make a change in the gain. No op amps are used in these cases.

**Table 1. Logic-Control Truth Table**

| DIGITAL INPUTS |    |      |

|----------------|----|------|

| D1             | D0 | GAIN |

| 0              | 0  | 1    |

| 0              | 1  | 2    |

| 1              | 0  | 4    |

| 1              | 1  | 8    |

Figure 1. Programmable Instrumentation Amplifier Using MAX5426

### **Applications Information**

The MAX5426 is ideal for programmable instrumentation amplifier applications. The typical application circuit of Figure 1 uses the MAX5426 in classical instrumentation amplifier configurations. Two digital inputs set the gain to 1, 2, 4, or 8.

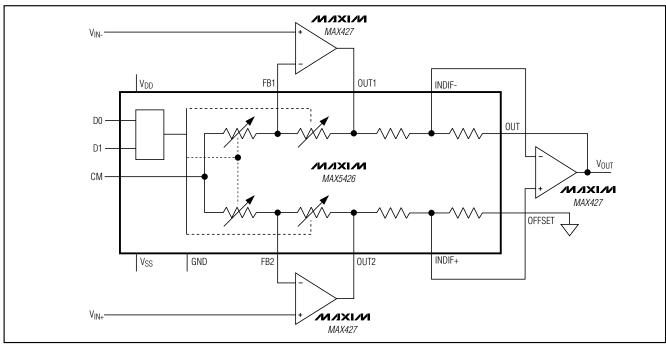

#### **Op Amp Selection Guidelines**

Selection of an op amp for instrumentation amplifier circuits depends on the accuracy requirements of the specific application. General guidelines are to choose an op amp with sufficient open-loop gain, low input-off-set voltage, and a high common-mode rejection ratio.

High open-loop gain is needed to increase the gain accuracy, while low input-offset voltage and low input-offset current help meet gain and offset requirements.

Other parameters such as low input capacitance, low input bias current, high input common-mode range, and low noise often need to be considered for a wide input voltage range stability and AC considerations. The MAX427 is an excellent choice to use with the MAX5426.

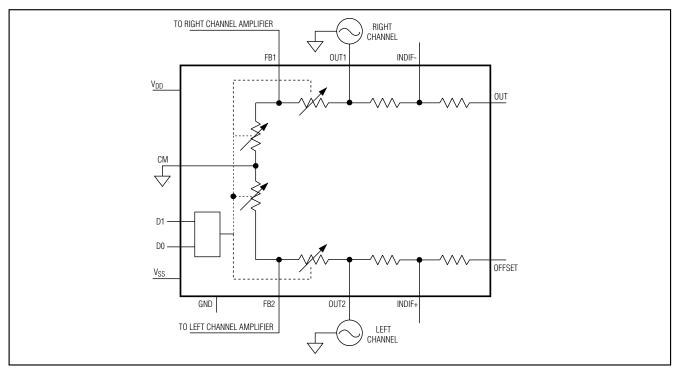

#### Stereo Audio-Taper Attenuator

Figure 2 shows the application of the MAX5426 as a dual attenuator that can be used in stereo audio systems.

#### **Power Supplies and Bypassing**

The MAX5426 operates from dual  $\pm 5V$  to  $\pm 15V$  supplies. In many applications the MAX5426 does not require bypassing. If power-supply noise is excessive, bypass V<sub>DD</sub> and V<sub>SS</sub> with 0.1 $\mu$ F ceramic capacitors to GND.

#### **Layout Concerns**

For best performance, reduce parasitic board capacitance by minimizing the circuit board trace from amplifier outputs to inverting inputs. Also choose op amps with low input capacitance.

Figure 2. Stereo Audio-Taper Attenuator

Figure 3. Timing Diagram

## **Functional Diagram**

## Pin Configuration

#### TOP VIEW 14 D1 V<sub>DD</sub> 1 13 D0 GND 2 V<sub>SS</sub> 3 MIXIM FB2 4 MAX5426 11 FB1 0UT2 5 10 OUT1 OFFSET 6 9 OUT 8 INDIF+ INDIF- 7

## \_Chip Information

TRANSISTOR COUNT: 126

PROCESS TECHNOLOGY: BICMOS

### Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.